- 您现在的位置:买卖IC网 > Sheet目录344 > MSC8126ADSE (Freescale Semiconductor)KIT ADVANCED DEV SYSTEM 8126

�� �

�

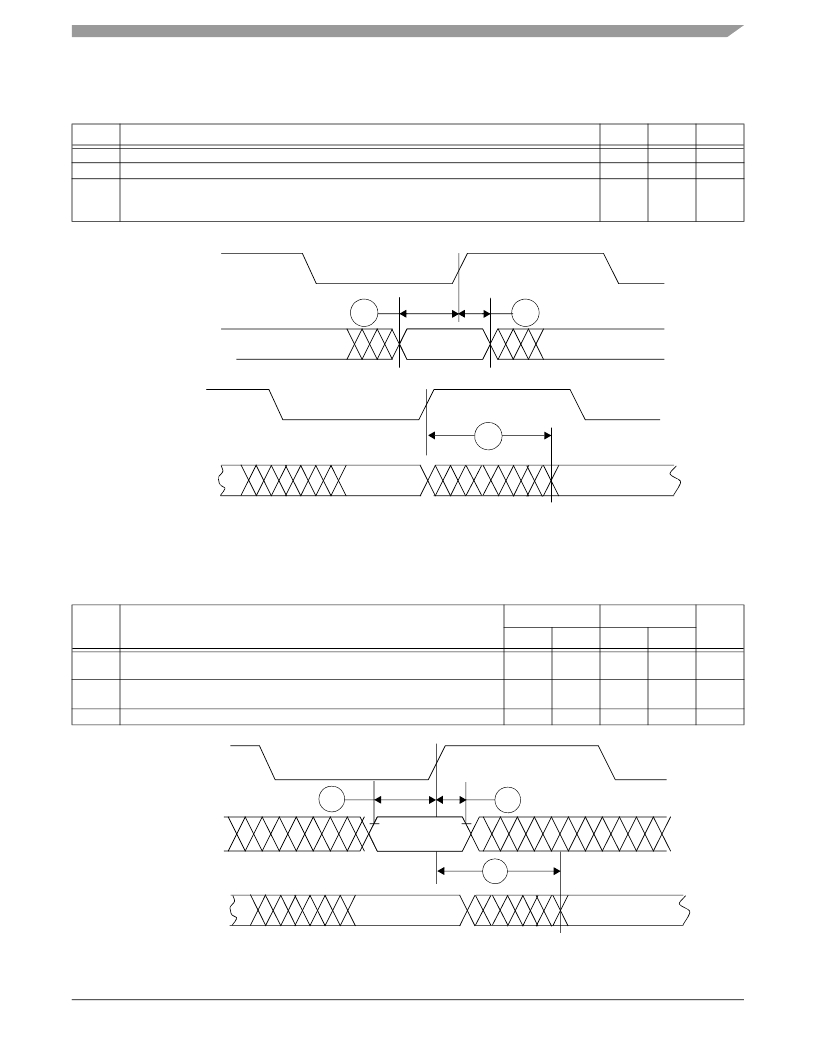

2.5.10.2�

�MII� Mode� Timing�

�Table� 25.� MII� Mode� Signal� Timing�

�No.�

�803�

�804�

�Characteristics�

�ETHRX_DV,� ETHRXD[0–3],� ETHRX_ER� to� ETHRX_CLK� rising� edge� set-up� time�

�ETHRX_CLK� rising� edge� to� ETHRX_DV,� ETHRXD[0–3],� ETHRX_ER� hold� time�

�Min�

�3.5�

�3.5�

�Max�

�—�

�—�

�Unit�

�ns�

�ns�

�805�

�ETHTX_CLK� to� ETHTX_EN,� ETHTXD[0–3],� ETHTX_ER� output� delay�

�?� 1.1� V� core�

�?� 1.2� V� core�

�1�

�1�

�14.6�

�12.6�

�ns�

�ns�

�ETHRX_CLK�

�ETHRX_DV�

�ETHRXD[0–3]�

�ETHRX_ER�

�803�

�Valid�

�804�

�ETHTX_CLK�

�805�

�ETHTX_EN�

�ETHTXD[0–3]�

�Valid�

�Valid�

�ETHTX_ER�

�Figure� 24.� MII� Mode� Signal� Timing�

�2.5.10.3� RMII� Mode�

�Table� 26.� RMII� Mode� Signal� Timing�

�1.1� V� Core�

�1.2� V� Core�

�No.�

�Characteristics�

�Unit�

�Min�

�Max�

�Min�

�Max�

�806�

�ETHTX_EN,ETHRXD[0–1],� ETHCRS_DV,� ETHRX_ER� to� ETHREF_CLK� rising�

�1.6�

�—�

�2�

�—�

�ns�

�edge� set-up� time�

�807�

�ETHREF_CLK� rising� edge� to� ETHRXD[0–1],� ETHCRS_DV,� ETHRX_ER� hold�

�1.6�

�—�

�1.6�

�—�

�ns�

�time�

�811�

�ETHREF_CLK� rising� edge� to� ETHTXD[0–1],� ETHTX_EN� output� delay.�

�3�

�12.5�

�3�

�11�

�ns�

�ETHREF_CLK�

�ETHCRS_DV�

�ETHRXD[0–1]�

�806�

�Valid�

�807�

�ETHRX_ER�

�811�

�ETHTX_EN�

�ETHTXD[0–1]�

�Freescale� Semiconductor�

�Valid�

�Figure� 25.� RMII� Mode� Signal� Timing�

�MSC8126� Quad� Digital� Signal� Processor� Data� Sheet,� Rev.� 15�

�Valid�

�35�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

MSC8144ADS

ADS FOR MSC8144 DEVICE

MSC8156EVM

EVAL MODULE FOR MSC8156 LC

MSL1060AW

IC LED DRIVER 6 STRING

MSL1061AV

IC LED DRIVER 6 STRING

MSL2041GU

IC LED DRIVER 4 STRING

MSL2100BR

IC LED DRIVER 8 STRING

MSL2160DQ

IC LED DRIVER 16 STRING

MSL2162DQ

IC LED DRIVER 16 STRING

相关代理商/技术参数

MSC8126MP8000

功能描述:DSP 16BIT 500MHZ MULTI 431FCPBGA RoHS:否 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:StarCore 标准包装:40 系列:TMS320DM64x, DaVinci™ 类型:定点 接口:I²C,McASP,McBSP 时钟速率:400MHz 非易失内存:外部 芯片上RAM:160kB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:0°C ~ 90°C 安装类型:表面贴装 封装/外壳:548-BBGA,FCBGA 供应商设备封装:548-FCBGA(27x27) 包装:托盘 配用:TMDSDMK642-0E-ND - DEVELPER KIT W/NTSC CAMERA296-23038-ND - DSP STARTER KIT FOR TMS320C6416296-23059-ND - FLASHBURN PORTING KIT296-23058-ND - EVAL MODULE FOR DM642TMDSDMK642-ND - DEVELOPER KIT W/NTSC CAMERA

MSC8126TMP6400

功能描述:DSP 16BIT 400MHZ MULTI 431FCPBGA RoHS:否 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:StarCore 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘

MSC8126TVT6400

功能描述:IC DSP QUAD 16B 400MHZ 431FCPBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:StarCore 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘

MSC8126VT8000

功能描述:IC DSP QUAD 16B 500MHZ 431FCPBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:StarCore 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘

MSC81325M

制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:RF & MICROWAVE TRANSISTORS AVIONICS APPLICATIONS

MSC81350M

制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:RF & MICROWAVE TRANSISTORS AVIONICS APPLICATIONS

MSC81400M

制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:RF & MICROWAVE TRANSISTORS AVIONICS APPLICATIONS

MSC81402

制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:RF & MICROWAVE TRANSISTORS GENERAL PURPOSE AMPLIFIERS APPLICATIONS